懸念は、基準クロックオシレータとAD9957のアナロググランドを直結したことで、基準クロックでPLLを揺さぶっていることになっているのでは?という点です。そこで、オシレータからクリスタルに置き換えと外付けSGの接続を試してみました。

クリスタルに置き換え

ジャンク箱にあった19.6608MHzクリスタルを取り付けてみました。基板のパターンを変更してXTAL_SELを有効、オシレータを休止にします。51逓倍として1002.7008MHzでPLLを動作させます。ご覧の通りクリスタルの配線が長すぎますから、そこは割り引いてみることにしますが、それでも細かなスプリアスがもじゃもじゃと生えています。

クリスタルに置き換え

出力100MHz(CENTER 200MHz, SPAN 400MHz)

出力100MHz(SPAN 1MHz)

外付けSGを接続

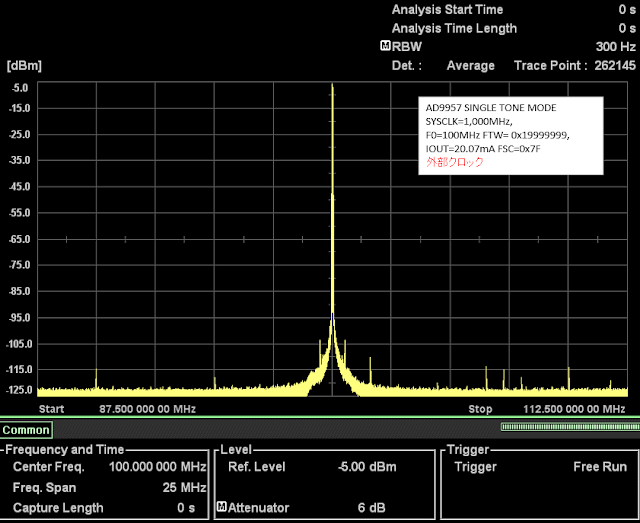

同軸ケーブルを直結してSGから1GHzを供給します。基板の消費電流は0.26Aでした。スプリアスの出方は私のイメージ通りです。スプリアスは当然ありますが、PLLを付く場合と比較すると、スッキリしています。

外付けSGからクロックを入力

出力400MHz(CENTER 500MHz, SPAN 1GHz)

出力400MHz(CENTER 250MHz, SPAN 500MHz)

出力100MHz(CENTER 250MHz, SPAN 500MHz)

出力100MHz(SPAN 25MHz)

出力30MHz(CENTER 100MHz, SPAN 200MHz)

出力20MHz(CENTER 100MHz, SPAN 200MHz)

出力10MHz(CENTER 100MHz, SPAN 200MHz)

NCO係数の影響は?

AD9957では、NCO出力が32ビットに対して波形テーブル入力は14ビットのようで位相の丸め誤差が発生します。それなら、NCO係数FTWの上位14ビットだけを使う場合と、下位ビットにも係数を与える場合とを比較すれば丸め誤差の影響を見られるのではないか?と試してみました。まずは、DDS出力125MHz(0x20000000)と101.55MHz(0x1A000000)です。これらのスプリアスは、丸め誤差とは無関係のものです。DACやトランス等の非直線性による、高調波や折り返し成分との混変調ではないかと考えます。

出力125MHz(FTW=0x20000000)

出力101.55MHz(FTW=0x1A000000)

次いでFTWの上位14ビットだけを使う場合と、下位ビットにも係数を与える場合とを比較してみます。下位ビットでは、スプリアスの周波数間隔が狭まっているように見えますが、明確に丸め誤差だと言えるようなスプリアス成分はよくわかりませんでした。下位ビットを使った途端、スプリアスがにょきにょき生えてくればわかりやすいですが、そんなことはありませんでした。

丸め誤差なし(0x20040000)

丸め誤差あり(0x20020000)

丸め誤差あり(0x20010000)

位相雑音について

DDSを通すと、位相雑音が低減するのか確認しました。10kHz以上はスペアナの測定限界なので1kHz以下に着目すると、確かに20 log(100/1000) = -20dB となっています。それはさておきSGの位相雑音が劣化してるような。

AD9957の位相雑音(出力100MHz)

SGの位相雑音(1GHz)

まとめ

AD9957内蔵のPLLがSFDR悪化を招いている原因だ!と思い込んでいましたが、広帯域SFDRは、クリスタル+PLLでもデータシートに近い特性が得られました。このため、クロックオシレータ+PLLのスプリアスが多いのは基板設計が課題であろうと再確認できました。次に外部SGからクロックを供給すると、SFDR値はクリスタル+PLLと概ね同じ結果となりました。ただ、PLLと比較して目につくスプリアスの数は少ないので、狭帯域SFDRは有利です。

0 件のコメント:

コメントを投稿