シリアルデータをつくるところと一緒に修正しました。

ついでに少しだけ説明も追加。

でも見ている人には、何やってるかさっぱりわからない気がします。ごめんなさい。

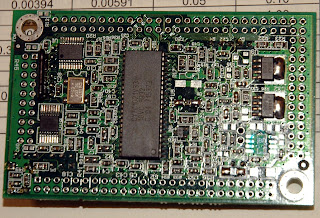

このテストベンチは、Texas InstrumentのPCM1803という24ビットの96ksps

A/Dコンバータに接続するシリ・パラ変換回路の動作確認のために作ったものです。

ここでは48kspsで動かすことを想定して、必要なクロックやシリアルデータをつくります。

テストベンチの出力

SDIN ・・・シリ・パラ変換回路にシリアルデータ信号(PCM1803の出力を想定)

CLK12M ・・・シリ・パラ変換回路に与えるクロック信号

CLK3M ・・・シリ・パラ変換回路に与えるクロック信号

CLK48K ・・・シリ・パラ変換回路に与えるクロック信号

RST ・・・シリ・パラ変換回路に与えるリセット信号

シリ・パラ変換回路の出力

LRCKO ・・・PCM1803に与えるLRクロック

BCKO ・・・PCM1803に与えるビットクロック

SCKO ・・・PCM1803に与えるシステムクロック

DOUT1 ・・・パラレルデータ出力(L)

DOUT2 ・・・パラレルデータ出力(R)

以下、テストベンチのコード

module tb_adc;

// Inputs

reg SDIN;

reg CLK12M;

reg CLK3M;

reg CLK48K;

reg RST;

// Outputs

wire BCKO;

wire LRCKO;

wire SCKO;

wire [23:0] DOUT1;

wire [23:0] DOUT2;

// Instantiate the Unit Under Test (UUT)

ADC_IF uut (

.SDIN(SDIN),

.BCKO(BCKO),

.LRCKO(LRCKO),

.SCKO(SCKO),

.CLK12M(CLK12M),

.CLK3M(CLK3M),

.CLK48K(CLK48K),

.DOUT1(DOUT1),

.DOUT2(DOUT2),

.RST(RST)

);

reg [5:0] i;

parameter DATA = 64'h0012_3456_0078_9ABC; // Lch(32bit)/Rch(32bit)

//・・・ MSBファースト、右詰めフォーマット

initial begin

// Initialize Inputs

SDIN = 0;

CLK12M = 1;

CLK3M = 1;

CLK48K = 1;

RST = 0;

i = 6'd63;

#8; // ・・・スタートしてから8ns後にリセット

RST = 1;

// Add stimulus here

#230; // ・・・さらに230ns後にリセットを解除

RST = 0;

end

always #40 begin //256fs 12.288MHz ・・・A/Dコンバータのシステムクロック

CLK12M = ‾CLK12M;

end

always #160 begin //64fs 3.072MHz ・・・ A/Dコンバータのビットクロック(BCK)

CLK3M = ‾CLK3M;

end

always #10240 begin //fs 48kHz

CLK48K = ‾CLK48K;

end

always #320 begin // ・・・320ns(ビットクロックの周期)毎にシリアルデータを出力

if (i == 6'd0) begin

i = 6'd63;

end else begin

i = i - 6'd1;

end

SDIN = DATA[i];

end

endmodule

こんなのでいいのかどうかわかりませんが、

とりあえずそれらしく動いてくれました。